技術講堂:門電路基礎

2020-3-13新聞

TTL門電路簡介:TTL電路采用(yòng)雙極型工藝制造,具有高(gāo)速度和(hé)品種多(duō)等特點。從六十年代開發成功第一代産品以來(lái)現有以下(xià)幾代産品。第一代TTL包括SN54/74系列,(其中54系列工作溫度爲-55℃~+125℃,74系列工作溫度爲0℃~+75℃),低功耗系列簡稱lttl,高(gāo)速系列簡稱HTTL。第二代TTL包括肖特基箝位系列(STTL)和(hé)低功耗肖特基系列(LSTTL)。第三代爲采用(yòng)等平面工藝制造的(de)先進的(de)STTL(ASTTL)和(hé)先進的(de)低功耗STTL(ALSTTL)。由于LSTTL和(hé)ALSTTL的(de)電路延時(shí)功耗積較小,STTL和(hé)ASTTL速度很快(kuài),因此獲得(de)了(le)廣泛的(de)應用(yòng)。

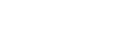

TTL反相器的(de)基本原理(lǐ)

帶電阻負載的(de)BJT反相器,其動态性能不理(lǐ)想。在保持邏輯功能不變的(de)前提下(xià),可(kě)以另外增加若幹元器以改善其動态性能,如減少由于BJT基區(qū)電荷存儲效應和(hé)負載電容所引起的(de)時(shí)延。這(zhè)需改變反相器輸入電路和(hé)輸出電路的(de)結構,以形成TTL反相器的(de)基本電路。下(xià)圖就是一個(gè)TTL反相器的(de)基本電路。

該電路由三部分(fēn)組成:

由三極管T1組成電路的(de)輸入級;

由T3、T4和(hé)二極管D組成輸出級;

由T2組成的(de)中間級作爲輸出級的(de)驅動電路,将T2的(de)單端輸入信号vI2轉換爲互補的(de)雙端輸出信号vI3和(hé)vI4,以驅動T3 和(hé)T4。

TTL反相器的(de)工作原理(lǐ)

(1)當輸入爲高(gāo)電平,如vI=3.6V時(shí),電源VCC通(tōng)過Rbl和(hé)T1的(de)集電結向T2、T3提供基極電流,使T2、T3飽和(hé),輸出爲低電平,如 vO=0.2V。此時(shí) VB1=VBC1+VBE2+VBE3=(0.7+0.7+0.7)V=2.1V

T1的(de)發射結處于反向偏置,而集電結處于正向偏置。所以T1處于發射結和(hé)集電結倒置使用(yòng)的(de)放大(dà)狀态。由于T2和(hé)T3飽和(hé),輸出 VC3 =0.2V,同時(shí)可(kě)估算(suàn)出VC2的(de)值:VC2=VCE2+VB3=(0.2+0.7)V=0.9V

此時(shí),VB4=VC2=0.9V。作用(yòng)于T4的(de)發射結和(hé)二極管D的(de)串聯支路的(de)電壓爲VC2-Vo=(0.9-0.2)V=0.7V,顯然,T4和(hé)D均截止,實現了(le)反相器的(de)邏輯關系:輸入爲高(gāo)電平時(shí),輸出爲低電平。

(2)當輸入爲低電平且電壓爲0.2V時(shí),T1的(de)發射結導通(tōng),其基極電壓等于輸入低電壓加上發射結正向壓降,即:VB1=(0.2+0.7)V=0.9V

此時(shí)VB1作用(yòng)于T1的(de)集電結和(hé)T2、T3的(de)發射結上,所以T2、T3都截止,輸出爲高(gāo)電平。

由于T2截止,VCC通(tōng)過RC2向T4提供基極電流,緻使T4和(hé)D導通(tōng),其電流流入負載。

輸出電壓爲vO=Vcc-VBE4-VD=(5-0.7-0.7)V=3.6V

同樣也(yě)實現了(le)反相器的(de)邏輯關系:輸入爲低電平時(shí),輸出爲高(gāo)電平。

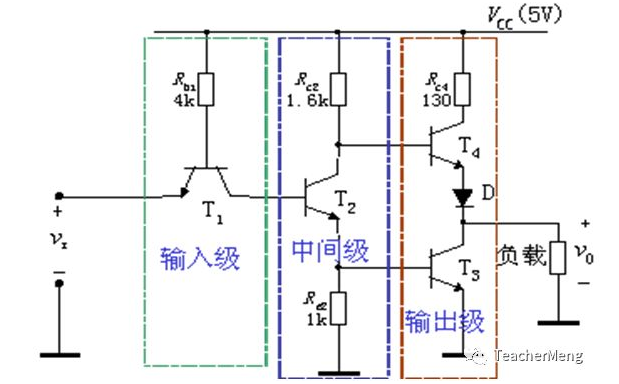

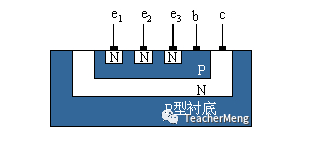

TTL與非門電路

基本TTL反相器不難改變成爲多(duō)輸入端的(de)與非門。它的(de)主要特點是在電路的(de)輸入端采用(yòng)了(le)多(duō)發射極的(de)BJT ,如下(xià)圖所示。器件中的(de)每一個(gè)發射極能各自獨立地形成正向偏置的(de)發射結,并可(kě)促使BJT進人(rén)放大(dà)或飽和(hé)區(qū)。兩個(gè)或多(duō)個(gè)發射極可(kě)以并聯地構成一大(dà)面積的(de)組合發射極。

下(xià)圖是采用(yòng)多(duō)發射極BJT用(yòng)作3輸入端TTL與非門的(de)輸入器件的(de)一個(gè)實例。當任一輸入端爲低電平時(shí),T1的(de)發射結将正向偏置而導通(tōng),T2将截止。結果将導緻輸出爲高(gāo)電平。隻有當全部輸入端爲高(gāo)電平時(shí),T1将轉入倒置放大(dà)狀态,T2和(hé)T3均飽和(hé),輸出爲低電平。

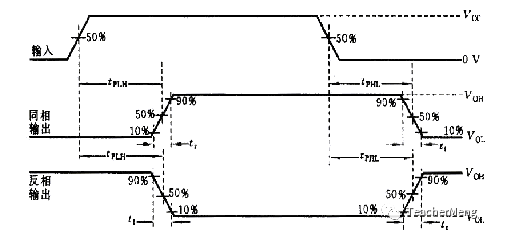

傳輸延遲時(shí)間

這(zhè)是一個(gè)表征門電路開關速度的(de)參數,意味著(zhe)門電路在輸入脈沖波形的(de)作用(yòng)下(xià),其輸出波形相對(duì)于輸入波形延遲了(le)多(duō)長(cháng)時(shí)間。

假設在門電路的(de)輸入端加入一脈沖波形、其幅度爲0~VCC(單位爲V)。相應的(de)的(de)輸出波形如下(xià)圖所示。通(tōng)常門電路輸出由低電平轉換高(gāo)電平或者由高(gāo)電平轉換到低電平所經曆的(de)時(shí)間分(fēn)别用(yòng)tPLH和(hé)tPHL表示,有時(shí)也(yě)采用(yòng)平均傳輸延遲時(shí)間這(zhè)一參數,即tPd=(tPLH+tPHL)/2。

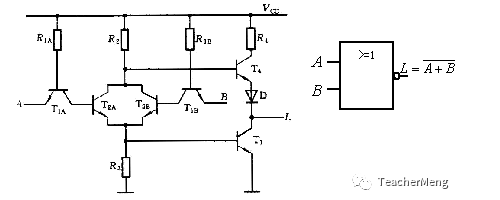

TTL或非門

下(xià)圖爲TTL或非門的(de)邏輯電路及其代表符号。

由圖可(kě)見,或非邏輯功能是對(duì)TTL與非門的(de)結構改進而來(lái),即用(yòng)兩個(gè)三極管T2A和(hé)T2B代替T2。

若兩輸入端爲低電平,則T2A和(hé)T2B均将截止,iB3=0,輸出爲高(gāo)電平。

若A、B兩輸入端中有一個(gè)爲高(gāo)電平,則T2A或T2B将飽和(hé),導緻iB3>0,iB3便使T3飽和(hé),輸出爲低電平。這(zhè)就實現了(le)或非功能。

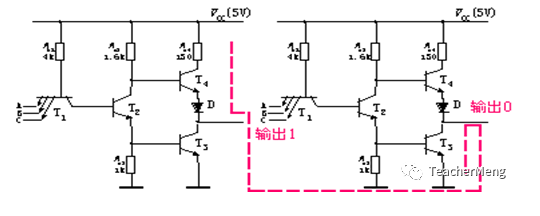

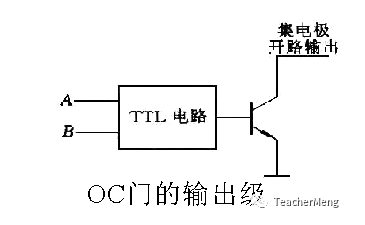

集電極開路門

在工程實踐中将兩個(gè)門的(de)輸出端并聯以實現與邏輯的(de)功能稱爲線與。

考察下(xià)圖所示的(de)情況。當将圖中所示的(de)兩個(gè)邏輯門的(de)輸出連接在一起,并且當第一個(gè)門的(de)輸出爲高(gāo)電平(第一個(gè)門的(de)T4導通(tōng)),第二個(gè)門的(de)輸出爲低電平(第二個(gè)門的(de)T3導通(tōng))時(shí),正如圖中紅線所示将出現一個(gè)大(dà)電流通(tōng)道,很可(kě)能導緻晶體管的(de)損壞。

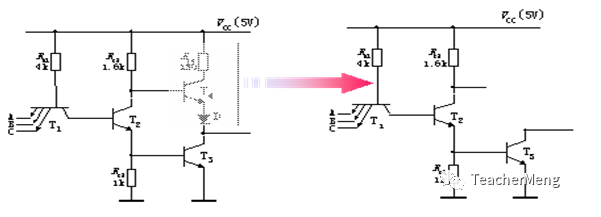

爲了(le)避免線與時(shí)的(de)産生大(dà)電流,可(kě)以采用(yòng)集電極開路門(簡稱OC門)來(lái)解決。所謂集電極開路是指從TTL與非門電路的(de)推挽式輸出級中删去電壓跟随器,如下(xià)圖所示:

對(duì)于一個(gè)兩輸入端的(de)OC門,其在電路中的(de)符号可(kě)用(yòng)下(xià)圖來(lái)表示:

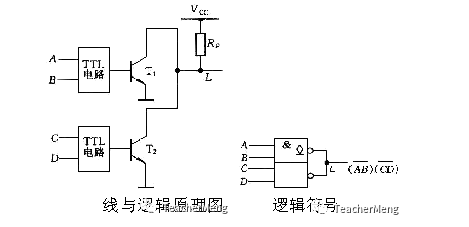

爲了(le)實現線與的(de)邏輯功能,可(kě)将多(duō)個(gè)門電路輸出管T3的(de)集電極至電源VCC之間,加一公共的(de)上拉電阻RP,如下(xià)圖所示。爲了(le)簡明(míng)起見,圖中以兩個(gè)OC門并聯爲例,其中圖标“”表示集電極開路之意。

上拉電阻Rp的(de)值可(kě)以這(zhè)樣來(lái)計算(suàn),主要考慮OC門必須驅動一定的(de)拉電流或灌電流負載。有關這(zhè)兩類負載的(de)概念前已討(tǎo)論,這(zhè)裏仍然适用(yòng),所不同的(de)是驅動門是由多(duō)個(gè)TTL門的(de)輸出端直接并聯而成。當OC門中的(de)一個(gè)TTL門的(de)輸出爲低電平,其他(tā)爲高(gāo)電平時(shí),灌電流将由一個(gè)輸出BJT(如T1或T2)承擔,這(zhè)是一種極限情況,此時(shí)上拉電阻RP具有限制電流的(de)作用(yòng)。爲保證IOL不超過額定值IOL(max),必須合理(lǐ)選用(yòng)RP的(de)值。例如VCC=5V,RP=1kΩ,則IOL=5mA。

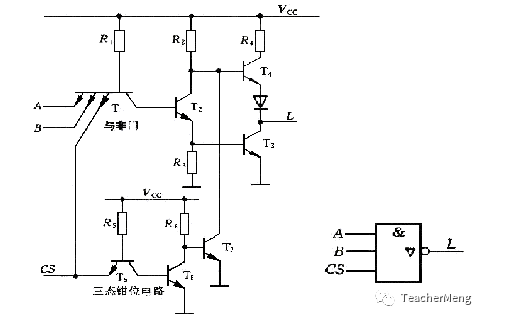

三态與非門(TSL)

利用(yòng)OC門雖然可(kě)以實現線與的(de)功能,但外接電阻Rp的(de)選擇要受到一定的(de)限制而不能取得(de)太小,因此影(yǐng)響了(le)工作速度。同時(shí)它省去了(le)有源負載,使得(de)帶負載能力下(xià)降。爲保持推拉式輸出級的(de)優點,還(hái)能作線與聯接,人(rén)們又開發了(le)一種三态與非門,它的(de)輸出除了(le)具有一般與非門的(de)兩種狀态,即輸出電阻較小的(de)高(gāo)、低電平狀态外,還(hái)具有高(gāo)輸出電阻的(de)第三狀态,稱爲高(gāo)阻态,又稱爲禁止态。

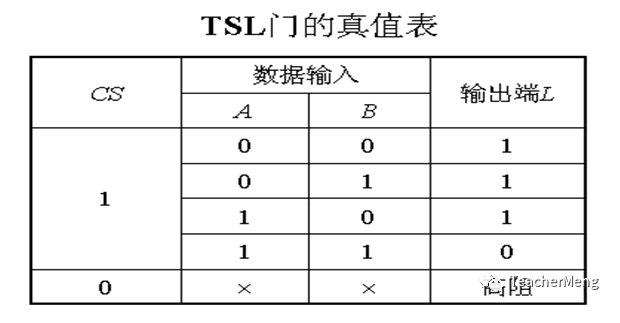

一個(gè)簡單的(de)TSL門的(de)電路如上圖所示。其中CS爲片選信号輸入端,A、B爲數據輸入端。

當CS=1時(shí),TSL門電路中的(de)T5處于倒置放大(dà)狀态,T6飽和(hé),T7截止,即其集電極相當于開路。此時(shí)輸出狀态将完全取決于數據輸入端A、B的(de)狀态,電路輸出與輸入的(de)邏輯關系與一般與非門相同。這(zhè)種狀态稱爲TSL的(de)工作狀态。

當CS=0時(shí)T7導通(tōng),使T4的(de)基極鉗制于低電平。同時(shí)由于低電平的(de)信号送到T1的(de)輸入端,迫使T2和(hé)T3截止。這(zhè)樣T3和(hé)T4均截止,門的(de)輸出端L出現開路,既不是低電平,又不是高(gāo)電平,這(zhè)就是第三工作狀态。這(zhè)樣,當CS爲高(gāo)電平時(shí),TSL門的(de)輸出信号送到總線,而當CS爲低電平時(shí),門的(de)輸出與數據總線斷開,此時(shí)數據總線的(de)狀态由其他(tā)門電路的(de)輸出所決定。

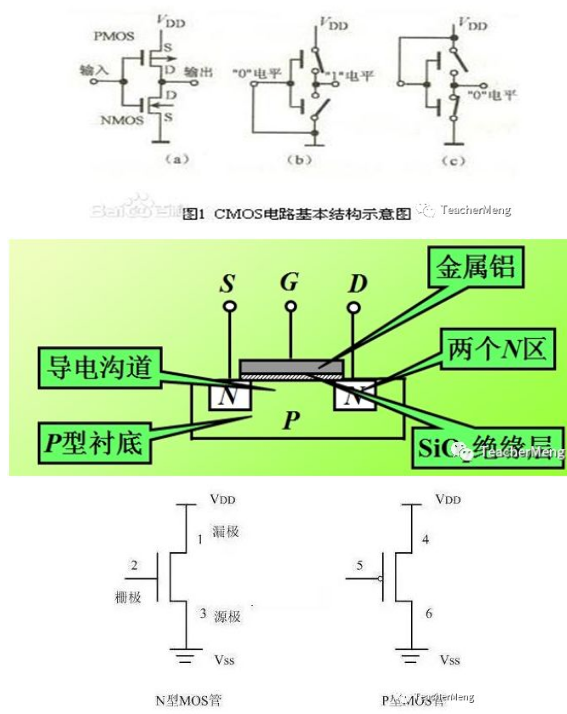

CMOS門電路簡介:CMOS電路是互補型金屬氧化(huà)物(wù)半導體電路(Complementary Metal-Oxide-Semiconductor)的(de)英文字頭縮寫,它由絕緣場(chǎng)效應晶體管組成,由于隻有一種載流子,因而是一種單極型晶體管集成電路,其基本結構是一個(gè)N溝道MOS管和(hé)一個(gè)P溝道MOS管。

CMOS工作原理(lǐ):由于兩管栅極工作電壓極性相反,故将兩管栅極相連作爲輸入端,兩個(gè)漏極相連作爲輸出端,如圖1(a)所示,則兩管正好互爲負載,處于互補工作狀态。當輸入低電平(Vi=Vss)時(shí),PMOS管導通(tōng),NMOS管截止,輸出高(gāo)電平,如圖1(b)所示。 ·當輸入高(gāo)電平(Vi=VDD)時(shí),PMOS管截止,NMOS管導通(tōng),輸出爲低電平,如圖1(c)所示。兩管如單刀(dāo)雙擲開關一樣交替工作,構成反相器。

CMOS邏輯電平

高(gāo)速CMOS電路的(de)電源電壓VDD通(tōng)常爲+5V;Vss接地,是0V。 高(gāo)電平視爲邏輯“1”,電平值的(de)範圍爲:VDD的(de)65%~VDD(或者VDD-1.5V~VDD)。低電平視作邏輯“0”,要求不超過VDD的(de)35%或0~1.5V。+1.5V~+3.5V應看作不确定電平。在硬件設計中要避免出現不确定電平。

近年來(lái),随著(zhe)亞微米技術的(de)發展,單片機的(de)電源呈下(xià)降趨勢。低電源電壓有助于降低功耗。VDD爲3.3V的(de)CMOS器件已大(dà)量使用(yòng)。在便攜式應用(yòng)中,VDD爲2.7V,甚至1.8V的(de)單片機也(yě)已經出現。将來(lái)電源電壓還(hái)會繼續下(xià)降,降到0.9V,但低于VDD的(de)35%的(de)電平視爲邏輯“0”,高(gāo)于VDD的(de)65%的(de)電平視爲邏輯“1”的(de)規律仍然是适用(yòng)的(de)。

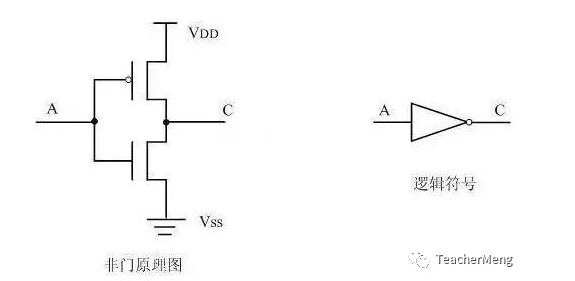

非門

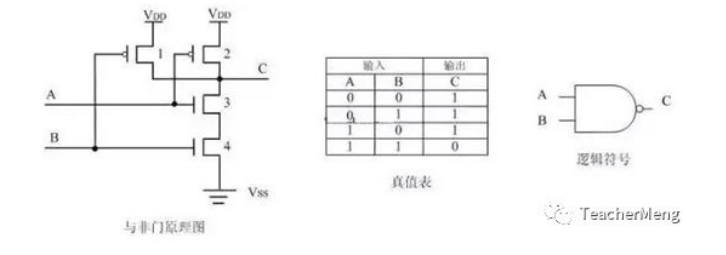

與非門

與非門工作原理(lǐ):

①、A、B輸入均爲低電平時(shí),1、2管導通(tōng),3、4管截止,C端電壓與VDD一緻,輸出高(gāo)電平。

②、A輸入高(gāo)電平,B輸入低電平時(shí),1、3管導通(tōng),2、4管截止,C端電位與1管的(de)漏極保持一緻,輸出高(gāo)電平。

③、A輸入低電平,B輸入高(gāo)電平時(shí),情況與②類似,亦輸出高(gāo)電平。

④、A、B輸入均爲高(gāo)電平時(shí),1、2管截止,3、4管導通(tōng),C端電壓與地一緻,輸出低電平。

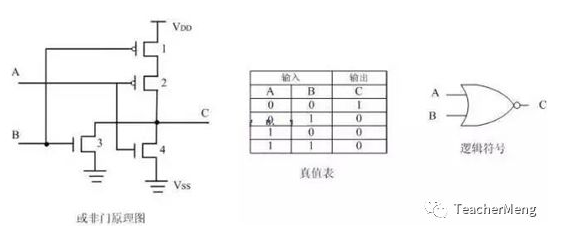

或非門

或非門工作原理(lǐ):

①、A、B輸入均爲低電平時(shí),1、2管導通(tōng),3、4管截止,C端電壓與VDD一緻,輸出高(gāo)電平。

②、A輸入高(gāo)電平,B輸入低電平時(shí),1、4管導通(tōng),2、3管截止,C端輸出低電平。

③、A輸入低電平,B輸入高(gāo)電平時(shí),情況與②類似,亦輸出低電平。

④、A、B輸入均爲高(gāo)電平時(shí),1、2管截止,3、4管導通(tōng),C端電壓與地一緻,輸出低電平。

注:将上述“與非”門、“或非”門邏輯符号的(de)輸出端的(de)小圓圈去掉,就成了(le)“與”門、“或”門的(de)邏輯符号。而實現“與”、“或”功能的(de)電路圖則必須在輸出端加上一個(gè)反向器,即加上一對(duì)CMOS管,因此,“與”門實際上比“與非”門複雜(zá),延遲時(shí)間也(yě)長(cháng)些,這(zhè)一點在電路設計中要注意。

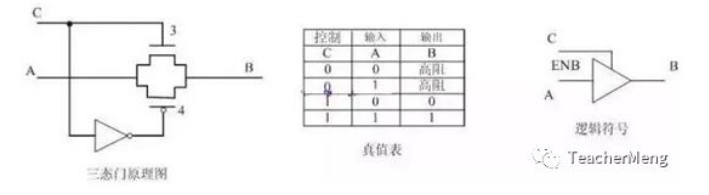

三态門

三态門的(de)工作原理(lǐ):

當控制端C爲“1”時(shí),N型管3導通(tōng),同時(shí),C端電平通(tōng)過反向器後成爲低電平,使P型管4導通(tōng),輸入端A的(de)電平狀況可(kě)以通(tōng)過3、4管到達輸出端B。

當控制端C爲“0”時(shí),3、4管都截止,輸入端A的(de)電平狀況無法到達輸出端B,輸出端B呈現高(gāo)電阻的(de)狀态,稱爲“高(gāo)阻态”。

這(zhè)個(gè)器件也(yě)稱作“帶控制端的(de)傳輸門”。帶有一定驅動能力的(de)三态門也(yě)稱作“緩沖器”,邏輯符号是一樣的(de)。

注:從CMOS等效電路或者真值表、邏輯表達式上都可(kě)以看出,把“0”和(hé)“1”換個(gè)位置,“與非”門就變成了(le)“或非”門。對(duì)于“1”有效的(de)信号是“與非”關系,對(duì)于“0”有效的(de)信号是“或非”關系。

上述圖中畫(huà)的(de)邏輯器件符号均是正邏輯下(xià)的(de)輸入、輸出關系,即對(duì)“1”(高(gāo)電平)有效而言。而單片機中的(de)多(duō)數控制信号是按照(zhào)負有效(低電平有效)定義的(de)。例如片選信号CS(ChipSelect),指該信号爲“0”時(shí)具有字符标明(míng)的(de)意義,即該信号爲“0”表示該芯片被選中。因此,“或非”門的(de)邏輯符号也(yě)可(kě)以畫(huà)成下(xià)圖。